**ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ

УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ

«ОРЕНБУРГСКИЙ ГОСУДАРСТВЕННЫЙ АГРАРНЫЙ УНИВЕРСИТЕТ»**

**МЕТОДИЧЕСКИЕ МАТЕРИАЛЫ ДЛЯ ОБУЧАЮЩИХСЯ

ПО ОСВОЕНИЮ ДИСЦИПЛИНЫ**

Б1.Б.14 Аппаратные средства вычислительной техники

**Направление подготовки (специальность) 10.03.01 Информационная безопасность**

**Профиль образовательной программы Безопасность автоматизированных систем**

**Форма обучения Очная**

## СОДЕРЖАНИЕ

|                                                                                              |           |

|----------------------------------------------------------------------------------------------|-----------|

| <b>1. Конспект лекций .....</b>                                                              | <b>3</b>  |

| <b>1.1 Лекция № 1 Арифметические основы ЭВМ.....</b>                                         | <b>3</b>  |

| <b>1.2 Лекция № 2 Логические основы построения ЭВМ.....</b>                                  | <b>22</b> |

| <b>1.3 Лекция №3 Структуры запоминающих устройств ЭВМ.....</b>                               | <b>37</b> |

| <b>1.4 Лекция №4 Структура ОЗУ.....</b>                                                      | <b>44</b> |

| <b>1.5 Лекция №5 Структура основной памяти.....</b>                                          | <b>55</b> |

| <b>1.6 Лекция №6 Структура машинных команд и способы адресации.....</b>                      | <b>61</b> |

| <b>1.7 Лекция №7 Принципы построения процессора.....</b>                                     | <b>80</b> |

| <b>2. Методические указания по проведению практических занятий .....</b>                     | <b>81</b> |

| <b>2.1 Практическое занятие № ПЗ-1 Выполнение операций в двоичном коде.....</b>              | <b>81</b> |

| <b>2.2 Практическое занятие № ПЗ-2 Минимизация логических функций.....</b>                   | <b>82</b> |

| <b>2.3 Практическое занятие № ПЗ-3 Аудиосистема ПК.....</b>                                  | <b>85</b> |

| <b>2.4 Практическое занятие № ПЗ-4 Коммуникационные устройства.....</b>                      | <b>88</b> |

| <b>2.5 Практическое занятие № ПЗ-5 Организация системы прерываний.....</b>                   | <b>88</b> |

| <b>2.6 Практическое занятие № ПЗ-6 Организация перехода к прерывающей<br/>программе.....</b> | <b>90</b> |

| <b>2.7 Практическое занятие № ПЗ-7 Принципы организации ввода-вывода</b>                     | <b>91</b> |

# 1. КОНСПЕКТ ЛЕКЦИЙ

## 1. 1 Лекция №1 (2 часа).

Тема: «Арифметические основы ЭВМ»

### 1.1.1 Вопросы лекции:

1. Введение в дисциплину.

2. Арифметические основы ЭВМ.

3. Перевод чисел из одной системы счисления в другую.

4. Формы представления чисел в ЭВМ.

5. Кодирование информации в ЭВМ.

6. Арифметические операции с двоичными числами.

### 1.1.2 Краткое содержание вопросов:

#### 1. Введение в дисциплину

Все современные ЭВМ имеют достаточно развитую систему команд, включающую десятки и сотни машинных операций. Однако выполнение любой операции основано на использовании простейших микроопераций типа сложения и сдвиг. Это позволяет иметь единое арифметико-логическое устройство для выполнения любых операций, связанных с обработкой информации.

#### 2. Арифметические основы ЭВМ

Подобные таблицы можно было бы построить для любой другой арифметической и логической операции (вычитание, умножение и т.д.), но именно данные этой таблицы положены в основу выполнения любой операции ЭВМ. Под знак чисел отводится специальный знаковый разряд. Знак “+” кодируется двоичным нулем, а знак “-” - единицей. Действия над прямыми кодами двоичных чисел при выполнении операций создают большие трудности, связанные с необходимостью учета значений знаковых разрядов:

Таблица 1.

#### Правила сложения двоичных цифр

| Значения двоичных чисел А и В |       |           | Разряд Суммы<br>$S_i$ | Перенос в следующий разряд<br>$P_i$ |

|-------------------------------|-------|-----------|-----------------------|-------------------------------------|

| $a_i$                         | $b_i$ | $P_{i-1}$ |                       |                                     |

| 0                             | 0     | 0         | 0                     | 0                                   |

| 0                             | 0     | 1         | 1                     | 0                                   |

| 0                             | 1     | 0         | 1                     | 0                                   |

| 0                             | 1     | 1         | 0                     | 1                                   |

| 1                             | 0     | 0         | 1                     | 0                                   |

| 1                             | 0     | 1         | 0                     | 1                                   |

| 1                             | 1     | 0         | 0                     | 1                                   |

| 1                             | 1     | 1         | 1                     | 1                                   |

- во-первых, следует отдельно обрабатывать значащие разряды чисел и разряды знака;

- во-вторых, значение разряда знака влияет на алгоритм выполнения операции (сложение может заменяться вычитанием и наоборот).

Во всех ЭВМ без исключения все операции выполняются над числами, представленными специальными машинными кодами. Их использование позволяет обрабатывать знаковые разряды чисел так же, как и значащие разряды, а также заменять операцию вычитания операцией сложения,

Различают **прямой код (П)**, **обратный код (ОК)** и **дополнительный код (ДК)** двоичных чисел.

### 3. Перевод чисел из одной системы счисления в другую

**Система счисления** - это способ записи чисел с помощью заданного набора специальных знаков (цифр).

Существуют позиционные и непозиционные системы счисления.

В **непозиционных с/с** вес цифры (т.е. тот вклад, который она вносит в общее значение числа) **не зависит от ее позиции в записи числа**. Так, в римской с/с в числе XXXII (тридцать два) вес цифры X в любой позиции равен просто десяти. Для обозначения основных чисел используются знаки:

I V X L C D M

1 5 10 50 100 500 1000

Остальные числа получаются как результат сложения или вычитания основных.

VL(45) CL1(151) MCMXCIII(1993)

В **позиционных с/с вес каждой цифры изменяется в зависимости от ее положения** (позиции) в последовательности цифр, изображающих число. Например, в числе 757,7 первая семерка обозначает 7 сотен, вторая - 7 единиц, третья - 7 десятых долей единиц.

Сама же запись числа 757,7 означает сокращенную запись выражения

$$700+50+7+0,7=7*10^2+5*10^1+7*10^0+7*10^{-1}$$

Любая позиционная с/с характеризуется своими базисом и основанием.

**Базис** - совокупность различных знаков или символов, используемых в позиционной с/с для записи чисел.

**Основание** - это количество различных знаков или символов, используемых для изображения цифр в данной системе.

За основание можно принять любое число - два, три, четыре и т.д. Следовательно, возможно **бесчисленное множество позиционных систем счисления**: двоичная, троичная, четверичная и т.д.

| Система счисления | Основание | Базис               |

|-------------------|-----------|---------------------|

| 2с/с              | 2         | 0,1                 |

| 5с/с              | 5         | 0,1,2,3,4           |

| 8с/с              | 8         | 0,1,2,3,4,5,6,7     |

| 10с/с             | 10        | 0,1,2,3,4,5,6,7,8,9 |

| 16с/с             | 16        | 0-9,A,B,C,D,E,F     |

Запись чисел в каждой из с/с с основанием “g” означает сокращенную запись выражения

$$a_{n-1}g^{n-1} + a_{n-2}g^{n-2} + \dots + a_1g^1 + a_0g^0 + \dots + a_{-m}g^{-m},$$

$a_i$  - цифры с/с;

$n$  и  $m$  - число целых и дробных разрядов соответственно.

Например,

$$1011,1_2 = 1*2^3 + 0*2^2 + 1*2^1 + 1*2^0 + 1*2^{-1}$$

$$276,52_8 = 2*8^2 + 7*8^1 + 6*8^0 + 5*8^{-1} + 2*8^{-2}$$

#### 4. Формы представления чисел в ЭВМ

\* двоичная (0,1)

\* восьмиричная (0,1,2,3,4,5,6,7)

\* шестнадцатиричная (0-9,A,B,C,D,E,F)

Использование 2 с/с в ЭВМ объясняется рядом причин:

\* для ее реализации нужны технические элементы с двумя возможными состояниями (есть ток-нет тока, намагничен-ненамагничен и т.п.);

\* представление информации посредством двух состояний надежно и помехоустойчиво;

\* возможно применение аппарата булевой алгебры для выполнения логических преобразований информации;

\* двоичная арифметика значительно проще десятичной;

\* двоичные таблицы сложения и умножения предельно просты.

Двоичная таблица сложения Двоичная таблица умножения

$$0+0=0 \quad 0*0=0$$

$$0+1=1+0=1 \quad 0*1=1*0=0$$

$$1+1=10 \quad 1*1=1$$

$$1+1+1=11 \quad 1*1*1=1$$

### **Почему используются 8 с/с и 16 с/с?**

Двоичная система, удобная для ЭВМ, для человека неудобна из-за громоздкости и непривычной записи.

Перевод чисел из 10 с/с в 2 с/с и наоборот выполняет машина. Однако, чтобы профессионально использовать ЭВМ, следует научиться понимать слово машины. Для этого и разработаны 8 с/с и 16 с/с.

Числа в этих с/с читаются почти так же легко, как и десятичные, требуют соответственно в три (8с/с) и в четыре (16с/с) раза меньше разрядов, чем в 2с/с (числа 8 и 16 соответственно 3-я и 4-я степени числа 2).

Перевод чисел из 8 с/с и 16 с/с в 2 с/с очень прост: достаточно каждую цифру заменить эквивалентной ей двоичной триадой (тройкой цифр) или тетрадой (четверкой цифр):

Например,

$$537,1_8=101\ 011\ 111,011_2$$

$$1A3,F_{16}=1\ 1010\ 0011,1111_2$$

Чтобы перевести число из 2с/с в 8с/с или 16с/с, нужно разбить влево и вправо от запятой на триады (для 8с/с) или тетрады (для 16с/с) и каждую такую группу заменить соответствующей 8-ричной или 16-ричной цифрой.

$$10101001,10111_2=10\ 101\ 001,\ 101\ 110_2=251,56_8$$

$$10101001,10111_2=1010\ 1001,\ 1011\ 1000_2=A9,B8_{16}$$

### **Перевод чисел из 10 с/с в 2с/с, 8 с/с, 16 с/с и др (Р-ую с/с).**

#### **Перевод целых чисел:**

\* Исходное число разделить на основание новой с/с (Р). Остаток от деления записать в новой с/с. Это младшая цифра искомого числа.

\* Если частное от деления равно 0, то искомое число получено

\* Если частное не равно 0, то разделить его на Р. Остаток от деления записать в новой с/с. Это предыдущая цифра искомого числа.

Число с основанием Р записывается как последовательность остатков от деления в обратном порядке, начиная с последнего.

### **Перевод правильных десятичных дробей:**

Правильную десятичную дробь при переводе необходимо последовательно умножать на основание той системы счисления, в которую она переводится, отделяя после каждого умножения целую часть произведения.

Число в новой с/с записывается как последовательность полученных целых частей произведения.

Умножение производится до тех пор, пока дробная часть произведения не станет равна 0. Это значит, что сделан точный перевод. В противном случае, перевод осуществляется до заданной точности.

### **Перевод смешанных чисел осуществляется в 3 этапа:**

- 1.Осуществляется перевод целой части числа в новую с/с.

- 2.Осуществляется перевод дробной части числа в новую с/с.

- 3.Складываются результаты переводов первых 2-х пунктов.

### **Перевод чисел из 2 с/с, 8 с/с, 16 с/с и т.д. (из Р-ой с/с) в 10 с/с.**

1. Записать переводимое число в виде полинома в старой с/с.

2. В полученном полиноме заменить основание и все коэффициенты числами в новой с/с (10 с/с).

3. Выполнить арифметические действия в новой (10-ой) с/с.

Например,

$$9B3_{17}=9*17^2+B*17^1+3*17^0=2791_{10}$$

$$\begin{aligned}110101,01_2 &= 1*2^5 + 1*2^4 + 0*2^3 + 1*2^2 + 0*2^1 + 1*2^0 + 0*2^{-1} + \\&+ 1*2^{-2} = 32 + 16 + 4 + 1 + 0,25 = 53,25_{10}\end{aligned}$$

## **5. Кодирование информации в ЭВМ**

*Кодирование* – операция, связанная с переходом от исходной формы представления информации в форму, удобную для хранения, передачи или обработки.

*Декодирование* – связано с обратным переходом к исходному представлению информации.

В настоящее время существуют разные способы кодирования и декодирования информации в компьютере.

Выбор способа зависит от вида информации, которую необходимо кодировать: текст, число, графическое изображение и т.д.

ЭВМ может обрабатывать информацию, представленную только в числовой форме. Любая другая информация (текстовая, графическая) преобразуется в числовую. Так, например, при вводе текста, каждый символ кодируется определенным числом (существуют специальные таблицы кодировки, наиболее известные и распространенные коды ASCII), а при выводе наоборот, каждому числу соответствует изображение определенного символа.

Восемь двоичных разрядов позволяют закодировать  $2^8=256$  символов, этого достаточно, чтобы закодировать любую букву, цифру или служебный символ. Нажатие клавиши на клавиатуре приводит к тому, что сигнал посыпается в компьютер в виде двоичного числа, которое хранится в кодовой таблице. **Кодовая таблица символов** – это внутреннее представление символов в компьютере. Во всем мире в качестве стандарта принята таблица ASCII (American Standard Code for Information Interchange) – Американский стандартный код для обмена информацией.

Первые 128 символов (от 0 до 127) – это цифры, прописные и строчные буквы латинского алфавита, управляющие символы. Вторая половина кодовой таблицы (от 128 до 255) предназначена для национальных символов (в том числе кириллицы), математических символов и так называемых псевдографических символов, которые используются для рисования рамок.

В разных странах, на разных моделях компьютеров могут использоваться и разные варианты второй половины кодовой таблицы.

Нужно иметь ввиду три особенности алфавита в кодовой таблице и их следствия:

- 1) прописные и строчные буквы представлены разными кодами, т.е. “A” и “a” – разные объекты;

- 2) при упорядочивании слов по алфавиту сравниваются между собой десятичные коды букв. Поэтому, чтобы избежать недоразумений, если не указано “нечувствителен к регистру”, используйте только латинский или русский алфавит и только прописные или только строчные первые буквы. Имейте ввиду, что любая цифра “меньше” любой буквы, код латинских букв “меньше” чем русских;

- 3) Многие латинские и русские буквы имеют визуально неразличимое начертание, но разные коды.

Итак, компьютер способен распознавать только значения бита. Однако он редко работает с конкретными битами в отдельности, а совокупность из 8 битов, воспринимаемая компьютером как единое целое, называется **байтом**.

Вся работа компьютера – это управление потоками байтов, которые устремляются в компьютер с клавиатуры или дисков (или по линии связи), преобразовываются по командам программ, запоминаются временно или записываются на постоянное хранение на магнитный диск, а также выводятся на экран дисплея или бумагу принтера в виде букв, цифр, значков.

## 6. Арифметические операции с двоичными числами

### Сложение

Вообще, сложение чаще всего заменяет все операции в ЭВМ, в том числе и вычитание, поэтому этот пункт будет самым большим, ибо нам надо разобрать все возможные случаи. Для примера будем брать 2 числа: А и В, которые будут менять свои значения в зависимости от примера. Стоит заметить, что все операции сложения чаще всего ведутся в обратных кодах. Не забываем, что у положительного числа все коды одинаковы.

Основные принципы сложения:

$$0 + 0 = 0$$

$$0 + 1 = 1$$

$$1 + 0 = 1$$

$$1 + 1 = 10$$

В последнем случае при сложении в столбик мы пишем 0, а 1 запоминаем. Все, как и в обычном сложении.

### Сложение в обратных кодах

#### Случай 1. А и В положительные числа.

При суммировании таких чисел просто складываются их обратные коды (которые равны прямым), включая знаковый разряд. Учитывая тот факт, что у положительных чисел знаковый разряд равен нулю, у суммы он также равен нулю, следовательно, число получается положительное.

$$13_{10} = 0000\ 1101_2 \text{ (ПК/OK)}$$

$$23_{10} = 0001\ 0111_2 \text{ (ПК/OK)}$$

$$\begin{array}{r}

0000\ 1101 \\

+\ 0001\ 0111 \\

\hline

0010\ 0100

\end{array}$$

$$(13+23)_{10} = 0010\ 0100_2 \text{ (ПК/OK)} = 36_{10}$$

**Случай 2. А — положительное, а В — отрицательное, по модулю больше А.**

В этом случае мы просто складываем числа А и В. Результат получаем, как обычно, в обратном коде:

$$13_{10} = 0000\ 1101_2 \text{ (ПК/OK)}$$

$$-23_{10} = 1001\ 0111_2 \text{ (ПК)} = 1110\ 1000_2 \text{ (OK)}$$

$$\begin{array}{r}

0000\ 1101 \\

+\ 1110\ 1000 \\

\hline

1111\ 0101

\end{array}$$

$$(13 + (-23))_{10} = 1111\ 0101_2 \text{ (OK)} = 1000\ 1010_2 \text{ (ПК)} = -10_{10}$$

**Случай 3. А — положительное, а В — отрицательное, по модулю меньше А.**

На первый взгляд, кажется, что этот случай не отличается от рассмотренного выше второго, однако, давайте посмотрим, что же получится в итоге:

$$-13_{10} = 1000\ 1101_2 \text{ (ПК)} = 1111\ 0010_2 \text{ (OK)}$$

$$23_{10} = 0001\ 0111_2 \text{ (ПК)}$$

$$\begin{array}{r}

1111\ 0010 \\

+\ 0001\ 0111 \\

\hline

1\ 0000\ 1001

\end{array}$$

Обратите внимание на результат. У нас выходит, будто сумма — отрицательное число (ибо в знаковом разряде единица), причем, цифр также больше. И, даже если бы не будем учитывать знак, а просто переведем модуль, то получим  $9_{10}$ , а не  $10_{10}$ , как должно быть.

Компьютер решает эту проблему, прибавляя получившуюся «лишнюю» единицу к получившемуся числу. Выглядит это следующим образом:

$$\begin{array}{r} 0000\ 1001 \\ +\ 0000\ 0001 \\ \hline 0000\ 1010 \end{array}$$

Как видите, в результате мы получили положительное число  $0000\ 1010_2$ , переведя которое в десятичную систему счисления мы получим  $10_{10}$ . А это и есть правильный ответ.

#### Случай 4. А и В отрицательные числа.

При таких условиях нам точно так же, как и в третьем случае, придется прибавлять единицу из знакового разряда к основному числу.

Проверим:

$$-13_{10} = 1000\ 1101_2 \text{ (ПК)} = 1111\ 0010_2 \text{ (OK)}$$

$$-23_{10} = 1001\ 0111_2 \text{ (ПК)} = 1110\ 1000_2 \text{ (OK)}$$

$$\begin{array}{r} 1111\ 0010 \\ +\ 1110\ 1000 \\ \hline 1\ 1101\ 1010 \end{array}$$

$$\begin{array}{r} 1101\ 1010 \\ +\ 0000\ 0001 \\ \hline 1101\ 1011 \end{array}$$

Переведем получившийся обратный код в десятичное число:  $1101\ 1011_2 \text{ (OK)} = 1010\ 0100_2 \text{ (ПК)} = -36_{10}$ . Как мы видим, ответ получился верным.

Однако, не всегда сложение проходит так гладко. Если вдруг числа у нас достаточно большие, то может возникнуть переполнение, то есть, результат не будет помещаться в выделенное для него место в памяти. Как вам понять, что возникло переполнение? Конечно, можно перевести число в десятичную систему счисления и проверить, больше ли модуль этого числа, чем максимально возможный. Однако, есть и другой способ. Если знак результата получается не таким, какой вы ожидали (не такой, как в примерах выше), значит, произошло переполнение.

К слову, «максимально возможный модуль» для чисел со знаком равен  $2^{n-1}$ , где  $n$  — количество бит, отведенных для хранения числа. Напомню, что в 1 байте 8 бит, в 2 байтах 16 бит и так далее. Получается, что если на хранение числа у вас отводится один байт, то максимально возможный модуль это  $2^{8-1} = 2^7 = 128$ . Если число у вас получается по модулю больше, значит, для операции требуется выделить на слагаемые больше памяти.

Отмечу, что переполнение может возникнуть только в том случае, когда оба числа положительны или отрицательны, ибо, когда знаки у них разные, модуль результата будет меньше как минимум одного слагаемого.

#### **Случай 5. Переполнение, когда А и В положительные.**

$$100_{10} = 0110\ 0100_2 \text{ (ПК/OK)}$$

$$30_{10} = 0001\ 1110_2 \text{ (ПК/OK)}$$

$$\begin{array}{r} 0110\ 0100 \\ + 0001\ 1110 \\ \hline 1000\ 0010 \end{array}$$

Заметьте, что, складывая два положительных числа, мы получили отрицательное. Следовательно — переполнение. Решается это, как я уже говорил, расширением диапазона:

$$100_{10} = 0000\ 0000\ 0110\ 0100_2 \text{ (ПК/OK)}$$

$$30_{10} = 0000\ 0000\ 0001\ 1110_2 \text{ (ПК/OK)}$$

$$\begin{array}{r} 0000\ 0000\ 0110\ 0100 \\ + 0000\ 0000\ 0001\ 1110 \\ \hline 0000\ 0000\ 1000\ 0010 \end{array}$$

Обратите внимание, что теперь в старшем разряде у нас 0, а значит, получили мы положительное число. И, естественно, результат верен:  $0000\ 0000\ 1000\ 0010_2 = 130_{10}$ .

#### **Случай 6. Переполнение, когда А и В — отрицательные.**

Тут та же история, что и в пятом случае. Убедимся в этом:

$$-100_{10} = 1110\ 0100_2 \text{ (ПК)} = 1001\ 1011_2 \text{ (OK)}$$

$$-30_{10} = 1001\ 1110_2 \text{ (ПК)} = 1110\ 0001_2 \text{ (OK)}$$

$$\begin{array}{r}

1001\ 1011 \\

+ 1110\ 0001 \\

\hline

1\ 0111\ 1100

\end{array}$$

Как обычно, убираем лишнюю единицу, прибавляя ее к результату:

$$\begin{array}{r}

0111\ 1100 \\

+ 0000\ 0001 \\

\hline

0111\ 1101

\end{array}$$

Итог: положительное число. Что делаем? Расширяем диапазон!

$$-100_{10} = 1000\ 0000\ 0110\ 0100_2 \text{ (ПК)} = 1111\ 1111\ 1001\ 1011_2 \text{ (OK)}$$

$$-30_{10} = 1000\ 0000\ 0001\ 1110_2 \text{ (ПК)} = 1111\ 1111\ 1110\ 0001_2 \text{ (OK)}$$

$$\begin{array}{r}

1111\ 1111\ 1001\ 1011 \\

+ 1111\ 1111\ 1110\ 0001 \\

\hline

1\ 1111\ 1111\ 0111\ 1100

\end{array}$$

$$\begin{array}{r}

1111\ 1111\ 0111\ 1100 \\

+ 0000\ 0000\ 0000\ 0001 \\

\hline

1111\ 1111\ 0111\ 1101

\end{array}$$

На этот раз получается отрицательное число. Значит, все верно.

### Сложение в дополнительных кодах

#### Случай 1. А и В — положительные числа.

В этом случае ничего не поменяется, ибо, как вы помните, у положительного числа прямой, обратный и дополнительный коды совпадают.

#### Случай 2. А — положительное, а В — отрицательное, по модулю больше А.

В этом случае мы получим верный результат, но уже в дополнительном коде. Оно и логично, складываем-то мы в дополнительном 😊

### Случай 3. А — положительное, а В — отрицательное, по модулю меньше А.

В случае с обратными кодами мы прибавляли лишнюю единицу к полученному коду. Здесь же нам придется ее просто отбрасывать. Давайте посмотрим:

$$-13_{10} = 1000\ 1101_2 \text{ (ПК)} = 1111\ 0010_2 \text{ (OK)} = 1111\ 0011_2 \text{ (ДК)}$$

$$23_{10} = 0001\ 0111_2 \text{ (ПК)}$$

$$\begin{array}{r} 1111\ 0011 \\ + 0001\ 0111 \\ \hline 1\ 0000\ 1010 \end{array}$$

$0000\ 1010_2$  — это уже  $10_{10}$ , а раз мы получили правильный ответ, то нам не нужна лишняя единица. Мы просто отбрасываем ее.

### Случай 4. А и В — отрицательные.

Здесь у нас два отрицательных числа, и оба в дополнительном коде, то есть, по логике вещей, результат у нас итак должен получиться в дополнительном коде.. но ведь у нас еще и единица там дополнительная, помните? Давайте взглянем, что же получится:

$$-13_{10} = 1000\ 1101_2 \text{ (ПК)} = 1111\ 0010_2 \text{ (OK)} = 1111\ 0011_2 \text{ (ДК)}$$

$$-23_{10} = 1001\ 0111_2 \text{ (ПК)} = 1110\ 1000_2 \text{ (OK)} = 1110\ 1001_2 \text{ (ДК)}$$

$$\begin{array}{r} 1111\ 0011 \\ + 1110\ 1001 \\ \hline 1\ 1101\ 1100 \end{array}$$

Взглянем на число, не учитывая «лишнюю единицу»:  $1101\ 1100_2 \text{ (ДК)} = 1101\ 1101_2 \text{ (OK)} = 1010\ 0010_2 \text{ (ПК)} = -36_{10}$ . Заметили? И без единицы у нас снова получился правильный ответ, поэтому мы просто отбрасываем единицу, как и в предыдущем примере, и ничего более не делаем.

**Пятый и шестой случаи — переполнение — для дополнительного кода аналогичны обратному.**

Стоит заметить, что перевод в дополнительный код для компьютера дольше, чем в обратный, ибо там не нужно прибавлять единицу. Однако, как вы смогли заметить,

отрицательные складывать легче в дополнительном коде, ибо нет лишнего прибавления единицы.

**Итог:** Стоит запомнить, что во всех случаях, кроме особого (случай 4, дополнительный код), если у вас получается лишняя единица — вы прибавляете ее к остальной части числа. И не забывайте про то, что если результат у вас получается не того знака, который вы ожидали — это переполнение.

## Вычитание

Любое вычитание сводится к сложению двух чисел, поэтому я не буду сейчас здесь разбирать все случаи подробно, а просто напишу про замену вычитания сложением.

### Случай 1. A и B — положительные.

$$A - B = A + (-B)$$

В итоге получаем сложение мы заменяем на вычитание, остается только проверить, меньше или больше абсолютная величина (модуль) B, чем A, для того, чтобы выбрать правильный способ решения.

### Случай 2. A — положительное, B — отрицательное.

Не имеет значения, какое B по модулю, больше или меньше A.

$$A - (-B) = A + B$$

Это тот случай, при котором возможно переполнение. Значит, если вы получаете отрицательное число в этом случае — переполнение.

### Случай 3. A — отрицательное, B — положительное.

$$-A - B = -A + (-B)$$

Получаем сложение двух отрицательных чисел. Это тоже случай, при котором возможно переполнение.

### Случай 4. A и B — отрицательные числа.

Получаем ситуацию аналогичную первой:

$$-A - (-B) = -A + B$$

Смотрим на модули чисел A и B, и решаем, как именно будем вычислять.

## Умножение

Вообще, умножение сложная операция, и специально для нее в компьютере имеется регистр, который называется «накапливающий сумматор» и с помощью последовательности сдвигов и сложений получается результат. Однако, мы умножаем по той же логике «в столбик», поэтому так и будем действовать.

Умножение в двоичной системе, на практике, получается быстрее, чем сложение и вычитание, ибо единственная сложность — много складывать, но всё сложение можно производить в прямом коде, а это значит, что нет всяких там «случаев», а все просто и понятно.

Определиться со знаком результата легко. Если знаковые разряды множителей были разными, то получится отрицательное число, то есть, «1» в знаке, иначе — «0». Если говорить еще более «заумно», то над знаковыми разрядами совершается операция сложения по модулю, она же «строгое (исключающее) ИЛИ», она же «XOR».

Попробуем умножить два числа:  $-13$  и  $23$ .

$$-13_{10} = 1000\ 1101_2 \text{ (ПК)}$$

$$23_{10} = 0001\ 0111_2 \text{ (ПК)}$$

$$\begin{array}{r} \times \quad \quad \quad 1 \quad \quad \quad 1101 \\ \quad \quad \quad 0 \quad \quad \quad 10111 \\ \hline \quad \quad \quad 1101 \\ \quad \quad \quad 1101 \\ \quad \quad \quad 1101 \\ \hline \quad \quad \quad 1101 \\ \hline 1 \quad \quad 100101011 \end{array}$$

Обратите внимание на несколько фактов:

- нули, содержащиеся между знаковым разрядом и первой единицей модуля числа писать нет смысла;

- ряды из нулей (при умножении «0» на первый множитель) тоже писать не надо, ведь не пишите их при обычном умножении в столбик? 😊

- полученный результат может занимать памяти больше, чем множители.

В результате у нас получилось число  $1\ 100101011_2$ , однако, давайте приведем его к нормальному виду:  $1\ 1\ 0010\ 1011_2$ . Но у нас нет записи числа в 10 цифр, только кратные байтам, то есть: 8 цифр, 16 цифр и так далее. В 8 это число уже никак не поместить, а вот в 16 в самый раз. Значит, что мы делаем? Мы добавляем нули между знаковым разрядом и модулем числа:  $1000\ 0001\ 0010\ 1011_2$ . Я выделил зеленым цветом добавленные мною нули.

Однако, давайте для примера возьмем два таких числа, чтобы в двоичной записи их были нули в младших разрядах. Например, перемножим 10 и 40:

$$10_{10} = 0000\ 1010_2 \text{ (ПК)}$$

$$40_{10} = 0010\ 1000_2 \text{ (ПК)}$$

$$\begin{array}{r}

\times \quad \quad \quad 101 \quad | \quad 0 \\

\quad \quad \quad 0 \quad \quad \quad 101 \quad \quad 000 \\

\hline

\quad \quad \quad 101 \\

\quad \quad \quad 101 \\

\hline

\quad \quad \quad 0 \quad \quad 11001 \quad | \quad 0000

\end{array}$$

Обратите внимание. При умножении подобных чисел, мы выравниванием их так, дабы младшие разряды, заполненные нулями, оказались справа, а умножаем только значимые части. Нули же потом просто дописываем в конце, столько, сколько их было. Как и при обычном умножении в столбик 😊

Нормализовав ответ, получаем:  $0000\ 0001\ 1001\ 0000_2$ . Проверим:  $256 + 128 + 16 = 400_{10}$ . Ответ верен.

В принципе, это все знания, которые вам потребуются для умножения целых чисел в двоичном коде. О дробных поговорим чуть позже.

## Деление

Этот раздел, как и в случае с десятичной системой счисления, можно разделить на три подраздела:

- деление без остатка;

- деление с остатком;

- деление с заданной точностью.

Первый случай самый «удачный». Остатка не остается тогда, когда делимое кратно делителю. Для примера возьмем два числа:

$$65_{10} = 0100\ 0001_2$$

$$13_{10} \equiv 0000\ 1101,$$

Разделим их, предварительно отбросив знаковый разряд и лишние, незначимые нули. Знак частного мы получаем так же, как и при умножении: знак делимого XOR знак делителя. В остальном все идентично обычному делению в столбик:

$$\begin{array}{r}

1000001 \quad | \quad 1101 \\

- \underline{1101} \quad | \quad 101 \\

\quad \quad 1101 \\

- \underline{1101} \\

\quad \quad \quad 0

\end{array}$$

Получили ответ:  $0000\ 0101_2 = 5_{10}$ .

Однако, при делении также возможен остаток. Например, найдем частное и остаток от деления этих чисел:

$$39_{10} = 0010\ 0111_2$$

$$4_{10} = 0000\ 0100_2$$

$$\begin{array}{r}

100111 \quad | \quad 100 \\

-100 \quad \quad | \quad 1001 \\

\hline

111 \\

-100 \\

\hline

11

\end{array}$$

Заметим, что  $11_2$  у нас уже не делится на  $100_2$ , ибо оно меньше, чем делитель. Следовательно — это остаток. Теперь у нас два варианта. Или записать ответ как: 0000 1001<sub>2</sub>(остаток: 0000 0011<sub>2</sub>), или продолжать делить дальше, пока не получим дробь:

$$\begin{array}{r|l}

100111 & 100 \\

-100 & \hline

& 1001,11 \\

& 111 \\

-100 & \hline

& 110 \\

-100 & \hline

& 100 \\

-100 & \hline

& 0

\end{array}$$

В результате получили при делении частное:  $1001,11_2$ . Можете проверить его с помощью перевода в двоичную систему, если считаете нужным 😊 Несмотря на то, что я сейчас пишу про операции над целыми числами, результат получился вещественным. Что ж поделаешь.

К слову, у деления с остатком возможны еще две вариации. Первая — периодическая дробь в частном. Для примера разделим  $68_{10}$  на  $5_{10}$ :

$$68_{10} = 0100\ 0100_2$$

$$5_{10} = 0000\ 0101_2$$

$$\begin{array}{r}

1000100 \quad | \quad 101 \\

- \underline{101} \quad | \quad 1101, \color{blue}{1001} \color{red}{1001} \\

\quad \quad 111 \\

- \underline{101} \\

\quad \quad 1000 \\

- \underline{101} \\

\quad \quad \color{blue}{110} \\

- \underline{101} \\

\quad \quad 1000 \\

- \underline{101} \\

\quad \quad \color{red}{110} \\

- \underline{101} \\

\quad \quad 1000 \\

- \underline{101}

\end{array}$$

Обратите внимание на голубые и оранжевые части деления. Они повторяются, и, судя по тому, как мы делили, будут повторяться и дальше. Вывод: результат стоит записать с периодом:  $1101.(1001)_2$

Вторая вариация деления с остатком — деление чисел с разным знаком. Вообще в теории деления натуральных чисел, остаток — число неотрицательное, однако, с целыми числами не все так однозначно. Давайте примем за данность, что у нас остаток может получаться отрицательным, ибо в учебных заведениях, чаще всего, именно так и преподают деление с остатком.

Для деления с остатком справедлива формула:

$$a = p \times b + q$$

где:

- $a$  — делимое;

- $b$  — делитель;

- $p$  — частное;

- $q$  — остаток.

Знак остатка *всегда такой же, как и знак делимого!*

Для интереса попробуем разделить два числа в десятичной системе счисления. Пусть первое будет отрицательным, например «-87», а второе положительным, например, «20»:

$$\begin{array}{r} 87 \mid 20 \\ -80 \mid 4 \\ \hline 7 \end{array}$$

Теперь немного поразмыслим. При делении отрицательного на положительное мы должны получить отрицательное число, следовательно, частное у нас не «4», а «-4», попробуем подставить эти числа в формулу:

$$-87 = -4 \times 20 + 7$$

Ответ выходит неверным, ведь в правой части получается «-73», а не ожидаемые «-87». Так и должно быть, ведь остаток у нас не такого же знака, как и делимое, следовательно, изменим его:

$$-87 = -4 \times 20 - 7$$

Теперь все верно. Закрепим нашу теорию на практике, поделив, например, «-23» на «13» с остатком. Напомню, что при записи в столбик мы не пишем знаки чисел. Их мы вычисляем потом отдельно.

$$13_{10} = 0000\ 1101_2 \text{ (ПК)}$$

$$-23_{10} = 1001\ 0111_2 \text{ (ПК)}$$

$$\begin{array}{r} 10111 \quad | 1101 \\ - 1101 \quad | 1 \\ \hline 1010 \end{array}$$

Остаток получился  $1010_2$ . Вычислим знак частного, применив операцию XOR к знакам делимого и делителя:

$$1 \text{ XOR } 0 = 1$$

Выходит, что частное у нас не  $0000\ 0001_2$ , а  $1000\ 0001_2$ . Учитывая то, что остаток от деления у нас по знаку должен совпадать с делимым, получим остаток равный:  $1000\ 1010_2$ .

Выполним проверку:

$0000\ 1101 \times 1000\ 0001 + 1000\ 1010$ . Выполним по действиям:

$$\begin{array}{r} \times \quad 0 \quad \quad \quad 1101 \\ \quad \quad 1 \quad \quad \quad 1 \\ \hline \quad \quad 1 \quad \quad \quad 1101 \end{array}$$

Результат умножения:  $1000\ 1101_2$ . Выполним сложение:

$$1000\ 1101_2 \text{ (ПК)} = 1111\ 0010_2 \text{ (OK)}$$

$$1000\ 1010_2 \text{ (ПК)} = 1111\ 0101_2 \text{ (OK)}$$

$$\begin{array}{r}

1111\ 0010 \\

+\ 1111\ 0101 \\

\hline

1\ 1110\ 0111

\end{array}$$

$$\begin{array}{r}

1110\ 0111 \\

+\ 0000\ 0001 \\

\hline

1110\ 1000

\end{array}$$

Переведем результат в прямой код и десятичную систему счисления, для проверки:

$$1110\ 1000 \text{ (OK)} = 1001\ 0111 \text{ (ПК)} = -23_{10}$$

Деление с остатком выполнено верно.

И напоследок хочется сказать про деление с заданной точностью. Вы можете встретить такое задание, как: «вычислить с точностью до шести знаков после запятой» или «с точностью до 0,000001», что, в принципе, одно и то же. Это значит, что вам нужно делить число до седьмого знака после запятой, после чего нужно взглянуть на него и правильно округлить число до шестого знака. То есть, если седьмой знак 0, то просто отсекаете его и все последующее, оставляя результат до шестого знака. Если же 1, то прибавляете 1 к шестому знаку, после чего отсекаете все, что идет после него.

## 1. 2 Лекция №2 (2 часа).

**Тема:** «Логические основы построение ЭВМ»

### 1.2.1 Вопросы лекции:

1. Общие сведения о дискретных автоматах.

2. Основные логические функции и элементы.

3. Основные законы (тождества) булевой алгебры.

4. Элементы памяти.

### 1.2.2 Краткое содержание вопросов:

#### 1. Общие сведения о дискретных автоматах.

Современная техника, особенно такие ее разделы, как вычислительные машины, машины автоматизированного контроля и управления, телемеханика, автоматическая телефония и т.д., базируется на применении так называемых дискретных устройств (автоматов).

В общем смысле дискретным устройством (ДУ) называется техническое устройство, предназначенное для преобразования входной информации, поступающей в виде дискретных сигналов, в выходную дискретную информацию по заранее заданной программе.

Дискретное устройство (ДУ) можно разделить на три основных части:

1. Управляющую часть – это элементы, непосредственно реагирующие на поступающие воздействия извне;

2. Управляемую часть – это элементы или цепи, создающие сигналы на выходах дискретного автомата;

3. Промежуточную часть – это элементы, зависящие как от входных сигналов, так и друг от друга и осуществляющие, как правило, запоминание поступающих сигналов и их последовательностей.

Кроме того, в дискретном автомате можно выделить вспомогательную часть, включающую различные детали, элементы или цепи, которые не влияют на переработку или передачу информации, но обеспечивают правильную работу устройства, согласование отдельных его частей и формирование параметров его сигналов.

В качестве промежуточной части в дискретных устройствах используются специальные элементы, которые способны сохранять свое состояние или выходной сигнал после того, как входной сигнал, вызвавший переход в это состояние, перестал действовать, а для вторичного изменения состояния или возврата в исходное состояние требуется новое входное воздействие. Эти элементы называются элементами памяти, типичными представителями которых являются широко применяемые триггеры типа D, T, JK и SR.

Элементы памяти принято выделять в отдельный блок, который называется блоком памяти или памятью дискретного автомата.

Часть схемы дискретного устройства, не содержащая элементов памяти, называется логическим преобразователем или комбинационным блоком, который помимо формирования выходных сигналов обеспечивает управление блоком памяти. Таким образом, по функциональному признаку логический преобразователь условно можно представить в виде двух отдельных блоков: блока формирования выходных сигналов и блока управления памятью (рис. 1).

Дискретные устройства, не содержащие элементов памяти, могут быть рассмотрены, как частный случай ДА с памятью.

Процесс функционирования ДУ заключается в том, что при подаче на его вход некоторой последовательности сигналов оно переходит из одного состояния в другое и формирует последовательность выходных сигналов.

Задачей разработчика является правильно описать работу дискретного устройства, для этого необходимо математически задать все его элементы.

Математической моделью подобных устройств является абстрактный автомат, работающий в некотором идеализированном дискретном времени. Термин “абстрактный” используется в связи с идеализацией времени, а так же абстрагирования от реальной физической природы входных и выходных сигналов, рассматривая их просто как буквы некоторого алфавита.

Абстрактный автомат определяется как шестикомпонентный кортеж , у которого:

1. - множество состояний автомата (алфавит состояний);

2. - множество входных сигналов (входной алфавит);

3. - множество выходных сигналов (выходной алфавит);

4. функция определяет состояние автомата в следующий момент времени  $t+1$  в зависимости от состояния автомата и входного сигнала в момент времени  $t$ . Другими словами, функция ставит в соответствие паре состояния – входной сигнал состояние , в которое он переходит из под действием сигнала , т.е. ;

5. функция выводов  $\lambda$ , вид которой приводит к разделению автоматов на два класса, получивших наибольшее распространение, - автоматы Мили и Мура. В автомате Мили функция  $\lambda$  ставит паре состояния – входной сигнал выходной сигнал , т.е. ; в автомате Мура функция  $\lambda$  в соответствие состоянию выходной сигнал , т.е. ;

6. - начальное состояние автомата (), в котором он находится в момент времени  $t=0$ .

Абстрактный автомат (рис.2) можно представить в виде черного ящика, который имеет один вход, один выход и работает в дискретном времени, принимающем целые неотрицательные значения  $t=0, 1, 2, \dots$ . В любой момент дискретного времени  $t$  автомат находится в некотором состоянии , причем в начальный момент времени ( $t=0$ ) он установлен в начальное состояние . Будучи в момент времени  $t$  в состоянии , автомат способен воспринять на своем входе сигнал . В соответствии с функцией выходов в этот же момент времени он выдаст выходной сигнал и в следующий момент времени ( $t+1$ ) согласно функции переходов перейдет в состояние . Если на вход автомата, установленного в начальное состояние , подавать некоторую последовательность входных сигналов  $z(0), z(1), z(2), \dots$  - входное слово, то на его выходе будут формироваться выходные сигналы  $w(0), w(1), w(2), \dots$  - выходное слово. Относя каждому входному слову соответствующее ему выходное слово, получаем отображение, индуцированное абстрактным автоматом. Комбинационные схемы (КС) так же можно представить в качестве абстрактного автомата с одним внутренним состоянием. Автоматы с числом внутренних состояний более одного составляют класс автоматов с памятью.

И так, что бы задать автомат, необходимо описать все компоненты его кортежа .

Среди многообразия различных способов задания автомата наибольшее распространение получили табличный и графический.

Автомат Мили задан в таблице №1, в которой каждый элемент , записанный на пересечении столбца и строки , определяется следующим образом: . Для указанной таблицы  $A=\{a_1, a_2, a_3, a_4\}, Z=\{z_1, z_2\}, W=\{w_1, w_2, w_3, w_4, w_5\}$ .

Автомат Мура задается таблицей №2, в которой каждому столбцу приписаны не только состояние , но и выходной сигнал , соответствующий этому состоянию, где ,  $A=\{a_1, a_2, a_3, a_4\}, Z=\{z_1, z_2\}, W=\{w_1, w_2, w_3\}$ .

Таблица 1

|       | $a_1$     | $a_2$     | $a_3$     | $a_4$     |

|-------|-----------|-----------|-----------|-----------|

| $z_1$ | $a_2/w_1$ | $a_2/w_1$ | $a_1/w_2$ | $a_1/w_4$ |

|       |           |           |           |           |

|-------|-----------|-----------|-----------|-----------|

| $z_2$ | $a_4/w_5$ | $a_3/w_3$ | $a_4/w_4$ | $a_3/w_5$ |

|-------|-----------|-----------|-----------|-----------|

Таблица 2

|       |       |       |       |       |

|-------|-------|-------|-------|-------|

|       | $w_3$ | $w_2$ | $w_3$ | $w_1$ |

|       | $a_1$ | $a_2$ | $a_3$ | $a_4$ |

| $z_1$ | $a_1$ | $a_3$ | $a_1$ | $a_4$ |

| $z_2$ | $a_2$ | $a_4$ | $a_4$ | $a_1$ |

Для частных автоматов Мили и Мура в таблицах на месте неопределенных состояний и выходных сигналов ставится прочерк.

Другим способом задания автомата является ориентированный граф, вершины которого соответствуют состояниям, а дуги переходам между ними. Дуга, направленная из вершины в вершину, задает переход в автомате из состояния в состояние . В начале каждой дуги пишется сигнал , который вызывает данный переход. Для графа автомата Мили (рис. 3а) выходной сигнал, формируется на переходе, записывается в конце дуги, а для автомата Мура (рис. 3б) - рядом с вершиной, в которой он формируется. Если переход в автомате производится под действием нескольких входных сигналов, то дуге графа, направленной из в , приписываются все эти входные и соответствующие выходные сигналы.

Следующим этапом проектировки ДУ является переход от абстрактного автомата к структурному, в котором уже учитывается структура входных и выходных сигналов, а так же внутренне устройство автомата на уровне структурных схем. На этом этапе синтеза автомат приняло представлять в виде двух частей – памяти и комбинационной схемы (КС). Память автомата состоит из предварительно выбранных элементов памяти – элементарных полных автоматов Мура, которые являются типовыми ДУ, иначе говоря, это совокупность функционально связанных элементов, обеспечивающих реализацию одной или нескольких операций, которые выполняются по специальным командам или непрерывно с момента включения устройства. Наиболее часто используемые элементы памяти, как уже отмечалось, это D, T, JK и SR триггеры.

В отличие от абстрактного автомата, имеющего один вход и один выход, на которые поступают сигналы во входном и выходном алфавитах, структурный автомат (рис. 4) имеет  $L$  входных и  $N$  выходных полюсов, на каждом из которых сигнал может принимать два значения 0 и 1. В этом случае каждому входному сигналу абстрактного автомата соответствует некоторый двоичный вектор () и . Для кодирования входных сигналов абстрактного автомата различными двоичными векторами должно быть выполнено условие , где означает ближайшее целое число, не меньшее .

Компоненты вектора () представляют собой набор значений переменных , поставленный во взаимно-однозначное соответствие символу алфавита  $Z$ . Предположим, что некоторая переменная может принимать в любом этом наборе значения как 0, так и 1, т.е. символ кодируется двумя двоичными векторами () и (). В этом случае будем считать, что закодирован одним троичным вектором (), в котором . Тогда компоненты любого такого вектора могут принимать значения из множества  $\{0,1,-\}$ , причем если , то в соответствующем наборе значений переменных безразлично, равно ли нулю или единице.

Аналогично, сигналу () абстрактного автомата соответствует некоторый двоичный вектор () и . Для кодирования входных сигналов абстрактного автомата различными двоичными векторами должно быть выполнено условие . Как и ранее, допустим, что рассмотренный вектор () может быть троичным и у него .

Идентично кодированию входных и выходных сигналов каждому состоянию () абстрактного автомата в структурном автомате поставим в соответствие двоичный вектор (),. Для кодирования состояний абстрактного автомата различными двоичными векторами должно быть выполнено условие . Допустим, что и в этом случае двоичный вектор () может быть заменен троичным, у которого .

Далее предположим, что каждому переходу абстрактного автомата из состояния в состояние по воздействием входного сигнала с выдачей выходного сигнала соответствует переход структурного автомата из состояния () в состояние () под воздействие входного сигнала () с выдачей выходного сигнала (). Изменение состояний элементов памяти на таком переходе происходит под действием сигналов на входах памяти автомата (рис. 5). Таким образом, после выбора элементов памяти и кодирования символов алфавитов  $Z, W$  и  $A$  синтез структурного автомата сводится к синтезу КС, реализующей функции:

Г

де - функции обратной связи от памяти автомата к его КС, а - функции возбуждения элементов памяти автомата. Далее остается применить правила и законы минимизации и привести полученные функции к Совершенной ДНФ (СДНФ).

Закодируем состояния, входные и выходные сигналы абстрактного автомата Мили, заданного таблицей №1, следующими кодами:

Заменим состояния, входные и выходные сигналы полученными входами, в результате чего получим совмещенную таблицу (таб. 3) переходов и выходов структурного автомата Мили. Обратите внимание, что в качестве элемента памяти используется D-триггер.

Таблица 3

|       | $T_1 T_2$ |         |         |         |

|-------|-----------|---------|---------|---------|

| $x_1$ | 00        | 01      | 10      | 11      |

| 0     | 01/ 000   | 01/ 000 | 00/ 001 | 00/ 011 |

| 1     | 11/ 100   | 10/ 010 | 11/ 011 | 10/ 100 |

Полученной табличной записи соответствует следующая ДНФ:

Следующий этап структурного синтеза построение логической схемы автомата на выбранной базе элементов.

Как правило, в технике используются ДУ большой сложности, условия функционирования которых вообще нельзя выразить на формализованном языке, либо эта формулировка оказывается чрезвычайно громоздкой. Анализируя задачи, решаемые сложными дискретными устройствами, не смотря на огромное их разнообразие не трудно

заметить, что процедура решения одной из них сводится к упорядоченному выполнению ограниченного числа определенных операций, таких, как хранение дискретной информации, ее кодирование, подсчет, суммирование, коммутация, сравнение, преобразование и т.д.

Следствием этого является то, что сложные дискретные автоматы возможно строить на основе сравнительно небольшого числа простых, так называемых типовых дискретных устройств (блоков).

Наиболее интересным представителем типовых ДУ является программируемая логическая матрица (ПЛМ).

Структура этого устройства считается фундаментальной, т.к. на базе ПЛМ были разработаны более универсальные дискретные блоки. В следующем разделе рассмотрим структуру, принципы работы ПЛМ и приведем пример реализации КС на ее базе.

## 2.Основные логические функции и элементы.

### Функция "НЕ", инвертор

Простейшим логическим элементом является инвертор, который просто изменяет значение входного сигнала на прямо противоположное значение. Его функция записывается в следующем виде:

$$F(x) = \bar{x} ,$$

где черта над входным значением обозначает изменение его значения на противоположное. То же самое действие можно записать при помощи таблицы истинности, приведённой в таблице 2.1. Так как вход у этого логического элемента только один, то его таблица истинности состоит только из двух строк.

Таблица 2.1 – Таблица истинности логического инвертора

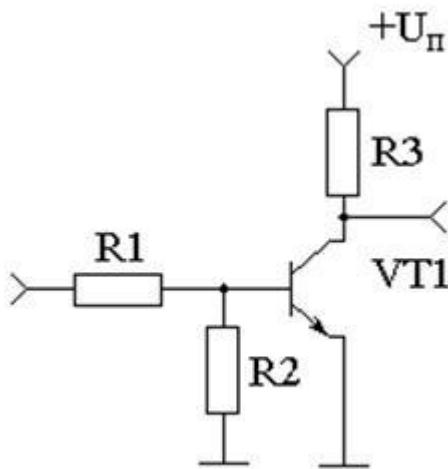

В качестве инвертора в простейшем случае можно использовать обычный усилитель с транзистором, включенном по схеме с общим эмиттером или истоком. Схема усилителя, выполненная на биполярном n-p-n транзисторе и позволяющая реализовать функцию логического инвертирования, приведена на рисунке 2.1.

Рисунок 2.1 – Схема, позволяющая реализовать функцию логического инвертирования

Схемы инверторов могут обладать различным временем распространения сигнала и могут работать на различные виды нагрузки. Они могут быть выполнены на одном или на нескольких транзисторах, но независимо от схемы и её параметров они осуществляют одну и ту же логическую функцию.

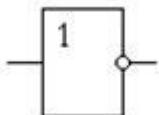

Для того чтобы особенности включения транзисторов не затеняли выполняемую функцию, для цифровых микросхем введены специальные условно-графические обозначения. Условно-графическое изображение инвертора приведено на рисунке 2.2.

Рисунок 2.2 – Условно-графическое изображение логического инвертора

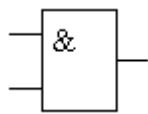

### Функция "И", логическое умножение

Следующим простейшим логическим элементом является схема, реализующая операцию логического умножения "И":

$$F(x_1, x_2) = x_1 \wedge x_2,$$

где символ  $\wedge$  обозначает функцию логического умножения (конъюнкцию). Иногда эта же функция записывается в другом виде:

$$F(x_1, x_2) = x_1 \wedge x_2 = x_1 \times x_2 = x_1 \& x_2$$

То же самое действие можно записать при помощи таблицы истинности, приведённой в таблице 2.2. В формуле, приведенной выше, использовано два аргумента. Поэтому элемент, выполняющий эту функцию, имеет два входа. Такой элемент обозначается "2И". Для элемента "2И" таблица истинности будет состоять из четырех строк. Количество строк таблицы истинности можно определить по формуле  $N = 2^n$ , где  $N$  — это количество строк в таблице истинности, а  $n$  — количество входов логического элемента. В нашем случае  $N = 2^2 = 4$ .

Таблица 2.2 – Таблица истинности схемы, выполняющей

логическую функцию "2И"

|   |   |  |

|---|---|--|

|   |   |  |

| 1 | 2 |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

Как видно из приведённой таблицы истинности активный сигнал на выходе этого логического элемента появляется только тогда, когда и на входе  $x_1$  и на входе  $x_2$  будут присутствовать логические единицы. То есть этот логический элемент действительно реализует операцию "И".

Условно-графическое изображение схемы, выполняющей логическую функцию "2И", на принципиальных схемах приведено на рисунке 2.3, и с этого момента схемы, выполняющие функцию "И", будут приводиться именно в таком виде. Это изображение не зависит от конкретной принципиальной схемы устройства, реализующей функцию логического умножения.

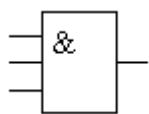

Рисунок 2.3 – Условно-графическое изображение схемы, выполняющей логическую функцию "2И"

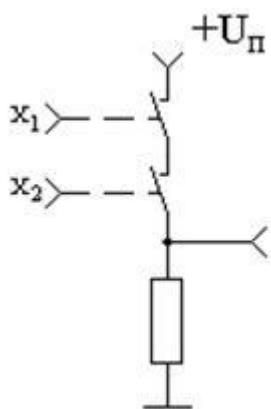

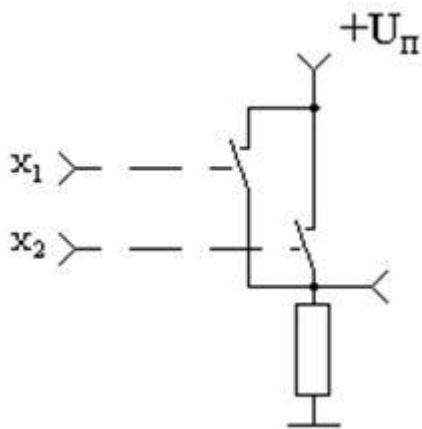

Проще всего понять, как работает такой элемент при помощи схемы, построенной на идеализированных ключах с электронным управлением, как это показано на рисунке 2.4. В приведённой схеме ток будет протекать только тогда, когда оба ключа будут замкнуты, а значит, единичный уровень на выходе схемы появится только при подаче на ее вход двух логических единиц.

Рисунок 2.4 – Эквивалентная схема, реализующая логическую функцию "2И"

Аналогично описывается и функция логического умножения трёх переменных:

$$F(x_1, x_2, x_3) = x_1 \wedge x_2 \wedge x_3$$

Её таблица истинности будет содержать уже восемь строк ( $2^3 = 8$ ). Таблица истинности трехходовой схемы логического умножения "3И" приведена в таблице 2.3, а условно-графическое изображение этого логического элемента на рисунке 2.5. При этом в схеме, построенной по принципу схемы, приведённой на рисунке 2.4, добавляется третий ключ.

Таблица 2.3 – Таблица истинности схемы, выполняющей

логическую функцию "3И"

| 1 | 2 | 3 |   |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

Рисунок 2.5 – Условно-графическое изображение схемы, выполняющей логическую функцию "ЗИ"

### 2.3 Функция "ИЛИ", логическое сложение

Следующим простейшим элементом является схема, реализующая операцию логического умножения "ИЛИ":

$$F(x_1, x_2) = x_1 \dot{U} x_2,$$

где символ  $\dot{U}$  обозначает функцию логического сложения (дизъюнкцию). Иногда эта же функция записывается в другом виде:

$$F(x_1, x_2) = x_1 \dot{U} x_2 = x_1 + x_2 = x_1 | x_2$$

То же самое действие можно записать при помощи таблицы истинности, приведённой в таблице 2.4. В формуле, приведенной выше, использовано два аргумента. Поэтому элемент, выполняющий эту функцию, имеет два входа. Такой элемент обозначается "2ИЛИ". Для элемента "2ИЛИ" таблица истинности будет состоять из четырех строк ( $2^2 = 4$ ).

Таблица 2.4 –Таблица истинности схемы, выполняющей логическую функцию "2ИЛИ"

|   |   |  |

|---|---|--|

|   |   |  |

| 1 | 2 |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

Как и в случае, рассмотренном для схемы логического умножения, воспользуемся для реализации схемы логического элемента "2ИЛИ" идеализированными ключами с электронным управлением. На этот раз соединим ключи параллельно. Эквивалентная схема, реализующая таблицу истинности 2.4, приведена на рисунке 2.6. Как видно из приведённой схемы, уровень логической единицы появится на её выходе, как только будет замкнут любой из ключей.

Рисунок 2.6 – Эквивалентная схема, реализующая логическую функцию "2ИЛИ"

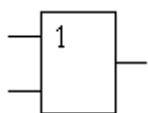

Так как функция логического суммирования может быть реализована устройствами, собранными по разным принципиальным схемам, то для обозначения этой функции используется свое условно-графическое обозначение. На условно-графическом изображении логического элемента "ИЛИ" используется специальный символ "1", как это приведено на рисунке 2.7.

Рисунок 2.7 – Условно-графическое изображение схемы, выполняющей логическую функцию "2ИЛИ"

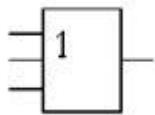

Подобным образом описывается и функция логического сложения трёх переменных:

$$F(x_1, x_2) = x_1 \dot{U} x_2 \dot{U} x_3$$

Её таблица истинности будет содержать уже восемь строк ( $2^3=8$ ). Таблица истинности трёхходовой схемы логического умножения "ЗИЛИ" приведена в таблице 1.5, а условно-графическое изображение на рисунке 2.8. В схеме, построенной по принципу схемы, приведённой на рисунке 2.6, придётся добавить третий ключ.

Рисунок 2.8 – Условно-графическое изображение схемы, выполняющей логическую функцию "ЗИЛИ"

Таблица 1.5 – Таблица истинности схемы, выполняющей логическую функцию "ЗИЛИ"

| 1 | 2 | 3 | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Теперь, после того, как мы рассмотрели принципы построения логических элементов, можно подробно остановиться на особенностях реализации логических элементов в различных схемотехнических решениях.

### 3.Основные законы (тождества) булевой алгебры.

Основными понятиями булевой алгебры являются понятия логической переменной и логической функции.

**Логической переменной** называется величина, которая может принимать одно из двух возможных состояний (значений), одно из которых обозначается символом "0", другое – "1" (для обозначения состояний возможно применение и других символов, например, "Да" и "Нет" и др.). Сами двоичные переменные чаще обозначают символами  $x_1, x_2, \dots$ . В силу определения логические переменные можно называть также двоичными переменными.

**Логической (булевой) функцией** (обычное обозначение  $-y$ ) называется функция двоичных переменных (аргументов), которая также может принимать одно из двух возможных состояний (значений): "0" или "1". Значение некоторой логической функции  $n$  переменных определяется или задается для каждого набора (сочетания) двоичных переменных. Количество возможных различных наборов, которые могут быть составлены из  $n$  аргументов, очевидно, равно  $2^n$ . При этом, поскольку сама функция на каждом наборе может принимать значение "0" или "1", то общее число возможных функций от  $n$  переменных равно  $2^{2^n}$ .

Таким образом, множество состояний (значений), которые могут принимать как аргументы, так и функции, равно двум. Для этих состояний в булевой алгебре определяются отношение эквивалентности, обозначаемое символом равенства (=) и три

операции: а) логического сложения (дизъюнкции), б) логического умножения (конъюнкции), в) логического отрицания (инверсии), обозначаемые соответственно символами:

+ или  $\vee$  - операция дизъюнкции,

• или  $\wedge$  или & - операция конъюнкции,

$\bar{*}$  - операция инверсии (\* - символ аргумента или функции).

Постулативно полагается, что при выполнении перечисленных операций отношения эквивалентности имеют вид:

а)  $0 + 0 = 0$ , б)  $0 \times 0 = 0$ , в)  $\bar{0} = 1$ ,

**(1)**  $0 + 1 = 1$ ,  $0 \times 1 = 0$ ,  $\bar{1} = 0$ .

$1 + 0 = 1$ ,  $1 \times 0 = 0$ ,

$1 + 1 = 1$ ;  $1 \times 1 = 1$ ;

На основании постулатов (1) можно вывести следующие соотношения (законы) алгебры логики:

1. Законы одинарных элементов (универсального множества – а), нулевого множества – б), тавтологии – в)):

**(2)** а)  $x + 1 = 1$ , б)  $x + 0 = x$ , в)  $x + x = x$ ,

$x \times 1 = x$ ;  $x \times 0 = 0$ ;  $x \times x = x$ .

2. Законы отрицания (двойного отрицания – а), дополнительности – б), двойственности – в)):

**(3)** а)  $\bar{\bar{x}} = x$  б)  $x + \bar{x} = 1$ , в)  $\overline{x_1 + x_2} = \bar{x}_1 \cdot \bar{x}_2$ ,

$x \cdot \bar{x} = 0$ ;  $\overline{\bar{x}_1 \cdot \bar{x}_2} = \bar{x}_1 + \bar{x}_2$ .

3. Законы абсорбции или поглощения – а) и склеивания – б):

**(4)** а)  $x_1 + x_1 \cdot x_2 = x_1$ , б)  $x_1 \cdot x_2 + x_1 \cdot \bar{x}_2 = x_1$ ,  $x_1 \cdot (x_1 + x_2) = x_1$ ;

$(x_1 + x_2) \cdot (x_1 + \bar{x}_2) = x_1$ .

Законы двойственности (3, в), называемые также законами деМоргана, были обобщены К. Шенном на случай произвольного (n) числа аргументов.

Кроме законов, перечисленных выше и не имеющих аналогов в обычной алгебре (алгебре чисел), для алгебры логики справедливы законы обычной алгебры: коммутативные или переместительные, дистрибутивные или распределительные, ассоциативные или сочетательные.

Любая логическая функция  $u$  на  $n$  двоичных переменных  $x_1, x_2, \dots, x_n$  может быть задана таблично. Такие таблицы, получившие название **таблицы истинности**, содержат  $2^n$  строк, в которые записываются все возможные двоичные наборы значений аргументов, а также соответствующее каждому из этих наборов значение функции.

#### 4. Элементы памяти.

Основой любого компьютера является ячейка памяти, которая может хранить данные или команды. Основой любой ячейки памяти является функциональное устройство, триггер (или защелка), которое может по команде принять или выдать один двоичный бит, а, главное, сохранять его. Триггер строится на основе базового набора логических схем (рис. 2.1.3.).

Рис. 3.1.3. Схема триггера в состоянии хранения бита информации.

1 и 2 – это два элемента «логическое НЕ», 3 и 4 – два элемента «логическое И-НЕ», которые представляют собой комбинацию логических элементов «И» и «НЕ». Такой элемент на входе выполняет операцию логического умножения, результат которой инвертируется на выходе логическим отрицанием. Триггер имеет два выхода  $Q$  и  $\bar{Q}$ . Сигнал на выходе  $Q$  соответствует значению, хранящемуся в триггере. Выход  $\bar{Q}$  используется для получения инверсного значения сигнала. Входы  $S$  и  $R$  предназначены для записи в триггер одного бита со значением 0 или 1.

Для записи в триггер 1 на вход  $S$  подается 1 (рис.2.1.4.). На выходе схемы 1 получится 0, который обеспечит на выходе схемы 3 единицу. С выхода схемы 3 единица поступит на вход схемы 4, на выходе которой значение изменится на ноль ( $\bar{R}=0$ ). Этот ноль на входе схемы 3 будет поддерживать сигнал на выходе в состоянии единицы. Теперь можно снять единичный сигнал на входе  $S$ , на выходе схемы 3 все равно будет высокий уровень, т.е. триггер сохраняет записанную в него 1. Единичный сигнал на входе 3 необходимо удерживать некоторое время, пока на выходе схемы 4 не появится нулевой сигнал. Затем на входе  $S$  вновь устанавливается нулевой сигнал, но триггер поддерживает единичный сигнал на выходе  $Q$ , т.е. сохраняет записанную в него единицу. Точно также, подав единичный сигнал на вход  $R$ , можно записать в триггер ноль.

Рис. 3.1.4. Запись в триггер единицы.

### 1. 3 Лекция №3 (2 часа).

Тема: «Структуры запоминающих устройств ЭВМ»

#### 1.3.1 Вопросы лекции:

1. Структуры адресных ЗУ

2. Элементы ЗУ с произвольным обращением

3. Постоянные ЗУ (ПЗУ, ППЗУ)

#### 1.3.2 Краткое содержание вопросов:

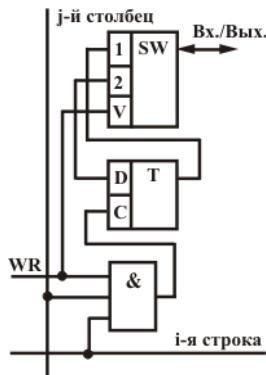

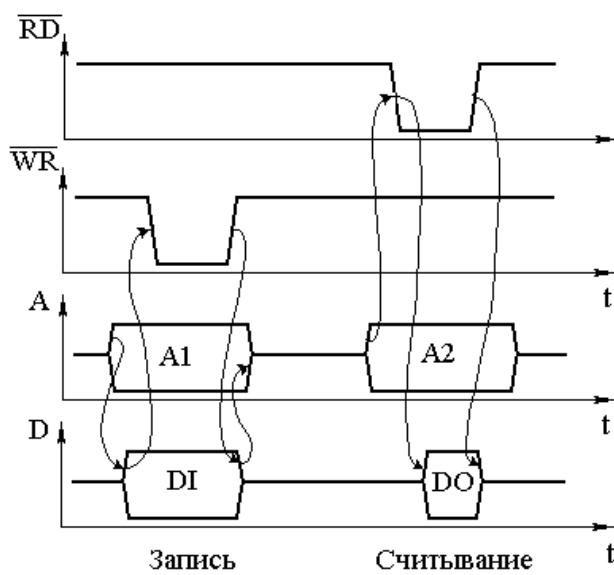

##### 1. Структуры адресных ЗУ

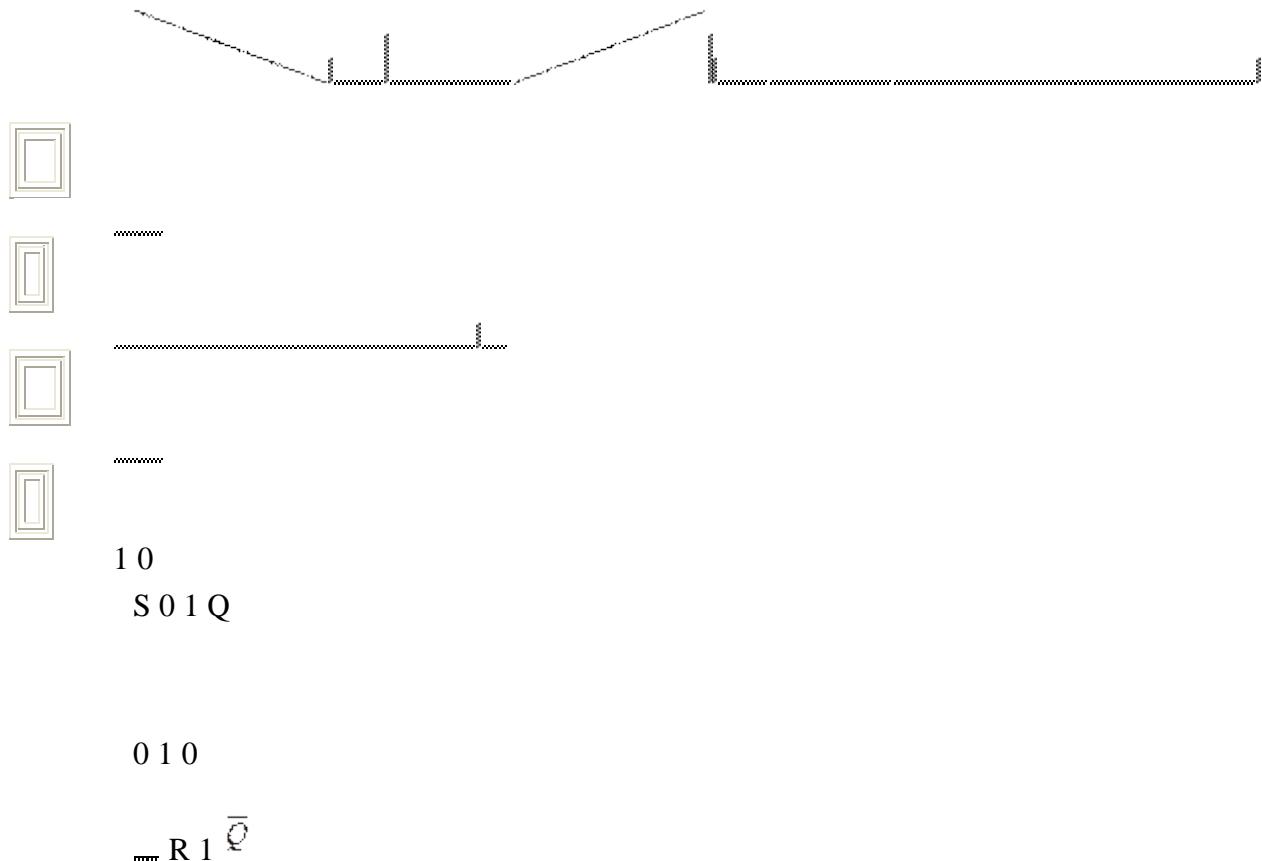

В полупроводниковых ЗУ адресного типа можно выделить две основные функциональные части: матрицу запоминающих элементов, обеспечивающую хранение данных, и схему выборки, обеспечивающую запись или считывание информации в выбранной ячейке памяти (рис. 4.2). Матрица ЗЭ – прямоугольная и в ранних образцах ЗУ имела размерность  $M = k \cdot m$ , где  $M$  – информационная емкость памяти в битах;  $k$  – число хранимых слов;  $m$  – их разрядность. Схема выборки состоит из дешифратора адресного кода  $DC$  и усилителей записи/считывания.

Рис. 4.2. Структура ЗУ типа 2D

Каждая строка матрицы ЗЭ соответствует ячейке памяти и хранит одно слово данных, а номера строк соответствуют адресам ячеек. Адрес выбранной ячейки по шине адреса поступает на все микросхемы памяти, но воспринимается только той микросхемой, на которую пришел разрешающий сигнал  $CS$  (*Chip Select* – выбор кристалла). С приходом сигнала  $CS$  дешифратор адресного кода активизирует одну из выходных линий, разрешая одновременный доступ ко всем элементам выбранной строки. Одноименные разряды всех ячеек образуют столбцы матрицы, соединяемые вертикальными линиями – внутренними линиями данных. Если осуществляется операция чтения, то состояния ЗЭ выбранной строки транслируются по этим линиям, усиливаются и выдаются на внешнюю шину данных. Если же выполняется операция записи, то усилители устанавливают на линиях уровни напряжения в соответствии с записываемыми данными, и ЗЭ переходят в соответствующие состояния "пуля" или "единицы". Подобная структура ЗУ получила название структуры 2D.

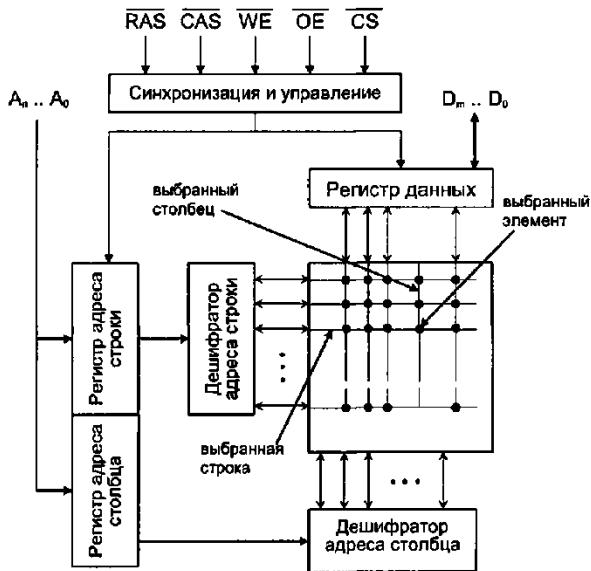

Структура 2D может быть использована только в ЗУ малой информационной емкости. С ростом емкости возрастает сложность дешифратора, поскольку число его выходных линий равно числу хранимых слов. Для ЗУ большой информационной емкости структура была усовершенствована, она получила название структуры **2DM**. На рис. 4.3 показана такая структура для ЗУ типа ROM. В ней возбужденный выход дешифратора **DCX** по-прежнему выбирает целую строку матрицы ЗЭ. Однако, в отличие от предыдущей структуры, длина строки не равна разрядности хранимых слов, а многократно ее превышает. Число строк матрицы, а значит, и число выходов дешифратора теперь меньше количества хранимых слов. Для выбора одной из строк служат не все разряды адресного кода, а их часть  $A_{n-1}, \dots, A_k$ . Остальные разряды адреса (от  $A_{k-1}$ , до  $A_0$ ) используются для того, чтобы выбрать необходимое слово из множества слов, содержащихся в этой строке. Это выполняется с помощью мультиплексоров, на адресные входы которых подаются коды  $A_{k-1}, \dots, A_0$ . Длина строки равна  $m2^k$ , где  $m$  – разрядность хранимых слов. Каждый отрезок строки длиной  $2^k$  хранит все одноименные (нулевые, первые, ...,  $m-e$ )разряды всех  $2^k$  слов этой строки. Из каждого такого отрезка мультиплексор выбирает один бит. Количество мультиплексоров соответствует количеству разрядов в слове. Таким образом, на выходах мультиплексоров формируется выходное слово. По разрешению сигнала **CS**, поступающего на входы **OE** управляемых буферов с тремя состояниями, выходное слово передается на внешнюю шину.

Структура **2DM** используется не только для ЗУ типа ROM, но и для ЗУ типа RAM с операциями чтения и записи. В этих ЗУ вместо мультиплексоров используются управляемые буфера данных, выполняющие не только функции мультиплексирования и выдачи данных в шину **DO**, но и функции приема данных пошине **DI** и формирования сигналов записи для соответствующих ЗЭ. Направление передачи данных определяется сигналом **R/W**, а управление буферами данных осуществляется дешифратором.

## 2. Элементы ЗУ с произвольным обращением

## Запоминающие устройства с произвольным обращением

В вычислительной технике в качестве ЗУ с произвольным обращением, используемых в оперативных памятях ЭВМ, применяются **полупроводниковые интегральные ЗУ**.

Полупроводниковые ЗУ имеют ряд важных достоинств: большее быстродействие, компактность, меньшую стоимость, совместимость по сигналам с логическими схемами, общие с другими электронными устройствами ЭВМ технологические и конструктивные принципы построения.

Недостатком полупроводниковых ЗУ с произвольным обращением является их энергозависимость, выражаяющаяся в том, что они потребляют энергию в режиме хранения информации и теряют информацию при выключении напряжения питания (потери информации можно избежать автоматическим переключением на аварийное питание от аккумуляторов).

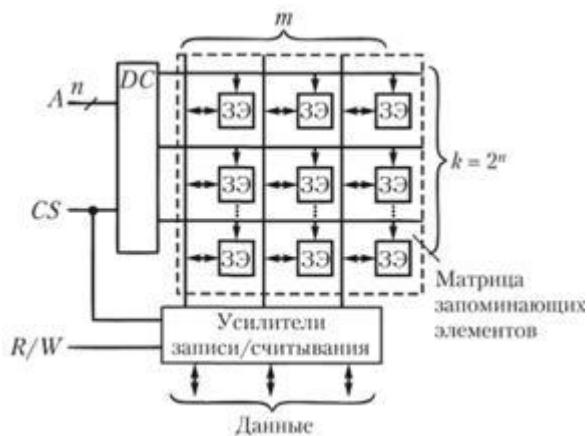

По типу ЗЭ различают биполярные ЗУ с биполярными транзисторами (с ТТЛ- или ЭСЛ-схемами) и МОП-ЗУ с МОП-транзисторами. В **биполярных интегральных ЗУ** в качестве ЗЭ используется статический триггер на двух многоэмиттерных транзисторах с непосредственными связями (рис. 4.9).

Рис. 4.9.

Запоминающий элемент

полупроводникового

биполярного ЗУ

Эмиттеры 11 и 21 являются парафазными информационными входами ЗЭ и служат для записи в триггер 1 или 0. Эти же эмиттеры используются как выходы при считывании информации. Адресные эмиттеры 12, 22, 13 и 23 образуют два конъюнктивно связанных входа выборки.

Организация ЗУ из

триггеров осуществляется по схеме типа ЗД. В режиме хранения (ЗЭ не выбран) эмиттерный ток открытого транзистора замыкается на землю через адресные эмиттеры и адресные линии (или только через один такой эмиттер и одну линию), находящиеся под потенциалом логического 0 ( $\leq 0,4$  В). При этом информационные эмиттеры должны быть заперты, для чего на них подается потенциал (1-1,5 В), который больше потенциала адресных эмиттеров (больше максимального значения уровня сигнала логического 0, равного 0,4 В, но меньше

минимального значения сигнала логической **1**, составляющего 2,4В), с тем чтобы при выборке ЗЭ через информационные эмиттеры протекали токи, необходимые для операций считывания и записи.

При выборке данного ЗЭ на его адресные эмиттеры с выходов адресных дешифраторов подается потенциал логической **1** ( $\geq 2,4$  В), превышающий потенциал информационных эмиттеров. Поэтому адресные эмиттеры оказываются запертыми, а коллекторный ток открытого транзистора течет через его информационный эмиттер, чем обеспечивается возможность считывания из ЗЭ и записи в него информации.

Состояния **1** и **0** ЗЭ распознаются по наличию тока соответственно в разрядной линии **1** (открыт транзистор  $T_1$ ) или в разрядной линии **0** (открыт транзистор  $T_2$ ).

Считывание происходит без разрушения информации. Хранимая в ЗЭ информация доступна для считывания все время, пока ЗЭ находится в выбранном состоянии, и в него не производится запись (отсутствует импульс «разрешение записи»).

При считывании на входы обоих усилителей записи подается потенциал логического **1**, в результате чего на выходах этих усилителей оказывается потенциал логической **1**, запирающий усилители записи и тем самым предотвращающий ответвление в них тока считывания (тока информационного эмиттера).

При считывании ток вытекает из информационного эмиттера открытого транзистора и втекает в базовую цепь входного транзистора соответствующего усилителя считывания, в результате чего выходной транзистор последнего полностью открывается.

Для записи в ЗЭ **1** или **0** с соответствующего усилителя записи на подключенный к нему информационный эмиттер подается потенциал логического **0** ( $\leq 0,4$  В), а на другой информационный эмиттер продолжает поступать с его невозбужденного усилителя записи потенциал, равный примерно 1,5В.

Если, допустим, производится запись **1** в триггер, находившийся перед этим в состоянии **1** (открыт транзистор  $T_2$ ), то подача потенциала низкого уровня на эмиттер 21 не меняет состояние триггера. Если до записи триггер находился в состоянии **0**, то при подаче потенциала низкого уровня на эмиттер 21 (запись 1) открывается транзистор  $T_2$ , при этом транзистор  $T_1$  закрывается и триггер устанавливается в состояние **1**.

Интегральная микросхема биполярного ЗУ представляет собой кристалл кремния, в котором образованы массив ЗЭ (триггеров) со всеми межсоединениями, а также адресные дешифраторы, усилители-формирователи записи и считывания и другие схемы для управления адресной выборкой, записью и считыванием. Для повышения быстродействия ЗУ эти обслуживающие схемы могут быть выполнены на основе ЭСЛ-элементов, работающих в линейной области, в то время как построенные на основе ТТЛ-элементов триггеры ЗЭ работают с насыщением. В таком случае кристалл содержит схемы согласования уровней сигналов для перехода от схем ТТЛ к схемам ЭСЛ и обратно.

Полупроводниковые ЗУ размещаются в стандартных корпусах интегральных микросхем. Число выводов ограничивают число слов и разрядов запоминающего массива интегральной микросхемы. Для получения ЗУ с большим числом разрядов и (или) слов, чем в запоминающем массиве в корпусе схемы, применяются несколько корпусов.

Данный вид памяти получил в современных ЭВМ название **SRAM** — это сокращение от Static RAM (Статическая оперативная память). Она названа так потому, что в отличие от динамической оперативной памяти (Dynamic RAM — DRAM), для сохранения ее содержимого не требуется периодическая регенерация. Преимущество памяти **SRAM** состоит не только в том, что не требуется регенерация, но и в том, что память SRAM имеет более высокое быстродействие, чем динамическая оперативная память, и может работать на той же частоте, что и современные процессоры.

Однако для хранения каждого бита в конструкции памяти SRAM используется кластер из шести транзисторов. Использование транзисторов без каких-либо конденсаторов означает, что нет необходимости в регенерации. (Ведь если нет никаких конденсаторов, то и заряды не теряются.) Пока подается питание, **SRAM** будет помнить то, что сохранено. Почему же тогда микросхемы **SRAM** не используются для всей системной памяти?

Это происходит потому, что по сравнению с динамической оперативной памятью, память <sup>^</sup> **SRAM** намного быстрее, но плотность ее намного ниже, а цена довольно высокая. Более низкая плотность означает, что микросхемы **SRAM**, имеют большие габариты, хотя их информационная емкость намного меньше. Например, емкость модуля динамической оперативной памяти может равняться 64 Мбайт или больше, в то время как емкость модуля **SRAM** приблизительно того же самого размера равна только 2 Мбайт; стоить он будет столько же, сколько тот же самый модуль динамической оперативной памяти емкостью 64 Мбайт. Таким образом, габариты памяти **SRAM** в среднем в 30 раз больше, и во столько же раз эта память дороже динамической оперативной памяти. Высокая стоимость и большие габариты не позволяют использовать память типа **SRAM** в качестве оперативной памяти в персональных компьютерах.

Даже притом, что память типа **SRAM** слишком дорога для использования в качестве оперативной памяти в персональных компьютерах, разработчики все-таки применяют ее с целью, значительного повышения эффективности ПК. Но чтобы избежать значительного увеличения стоимости, устанавливают только небольшой объем высокоскоростной памяти **SRAM**, которая используется в качестве кэш-памяти.

<sup>^</sup> **Динамические МОП-ЗУ** сравнительно дешевы, потребляют небольшую мощность, позволяют достигнуть очень высокой плотности размещения ЗЭ на кристалле и, следовательно, большей емкости в одном корпусе микросхемы. В настоящее время динамические МОП-ЗУ широко используются для построения основной (оперативной) памяти ЭВМ.

В динамических ЗУ двоичные коды хранятся на «запоминающих емкостях», в качестве которых используются паразитные емкости некоторых цепей схем. Примем, что отсутствие заряда на запоминающей емкости означает состояние **0**, а наличие — состояние **1**. В таком случае считывание информации состоит в определении, заряжены или нет запоминающие емкости.

Запоминающая емкость может неопределенно долго сохранять состояние <sup>^</sup> **0** (разряд отсутствует), но только ограниченное время из-за утечки заряда — состояние **1**. Поэтому в рассматриваемых ЗУ необходимо периодически (примерно через каждые 2 мс) производить восстановление хранимой информации. Операция динамического восстановления информации называется **рефреш**. Рассматриваемые ЗУ получили название динамических.

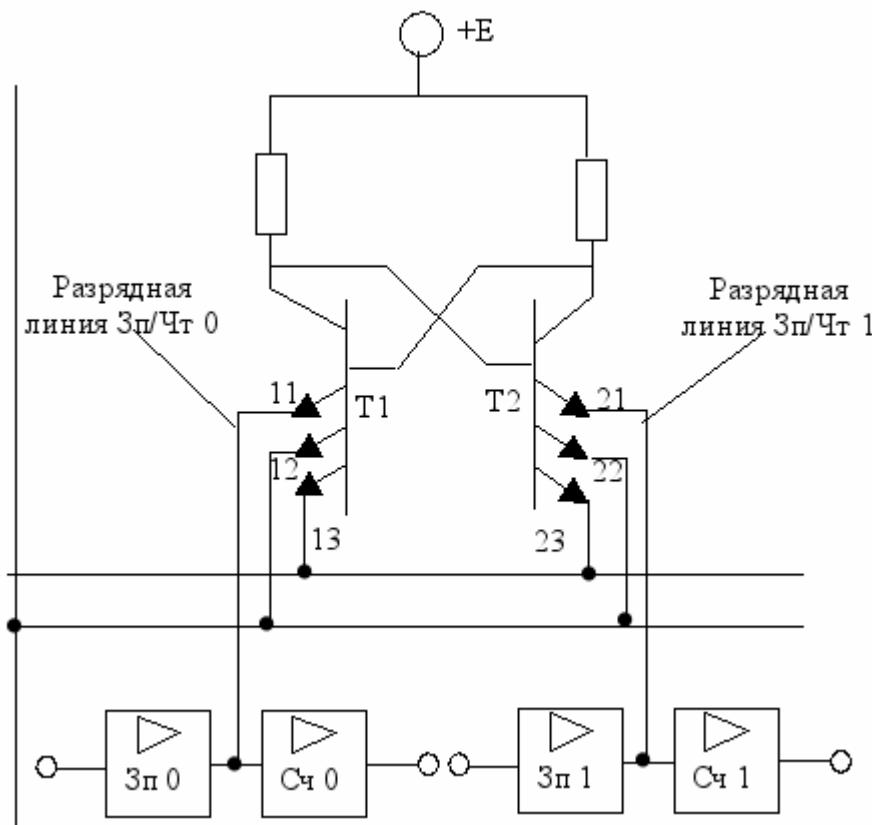

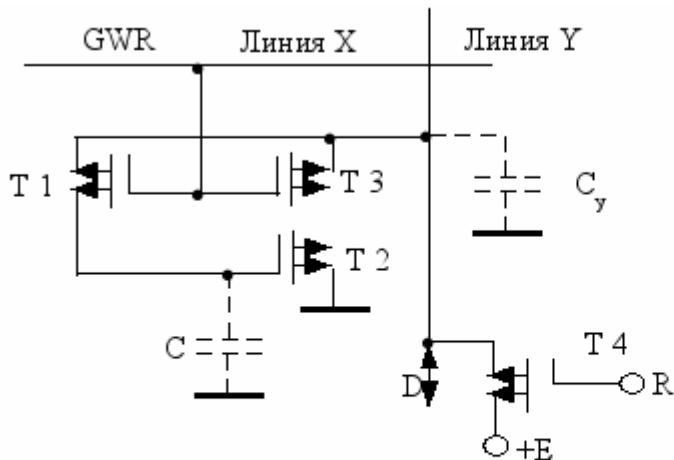

Схема динамического ЗУ на МОП-транзисторах в памяти со структурой 2D-М представлены

на рис. 4.10. Запоминающей емкостью служит паразитная емкость  $C$  затвора транзистора  $T_2$ . Линия разрядно-адресного коммутатора  $Y$  используется для ввода в ЗЭ бита информации при записи и съема его при считывании (см. рис. 4.8). Так как ЗЭ использует источник питания только при считывании, то им может служить паразитная емкость  $C_Y$  линии  $Y$ .

Предварительно перед считыванием от разрядно-адресного коммутатора подается сигнал  $R$ , с помощью которого подготавливается считывание с мультиплексированием для ЗЭ, выбираемых линией разрядно-адресного

Рис 4.10. Принципиальная электрическая схема динамического МОП - ЗУ

формирователя. Сигнал  $^R$  открывает транзистор  $T_4$ , и емкость  $C_Y$  подзаряжается от источника. Затем на линию  $X$  подается от адресного формирователя сигнал считывания - промежуточный уровень сигнала  $CWR$ , который открывает транзистор  $T_3$ , но не может открыть  $T_2$ . Если ЗЭ хранит **1**, то конденсатор  $C$  заряжен и открыт транзистор  $T_2$ . В этом случае через открытые транзисторы  $T_3$  и  $T_2$  конденсатор  $C_Y$  разряжается и низкий уровень (уровень **0**) сигнала  $D$  на линии  $Y$  указывает, что ЗЭ хранил инверсное значение, т.е. **1**. Если ЗЭ хранит **0**, то емкость  $C$  разряжена,  $T_2$  закрыт и сигнал  $CWR$  не может вызвать разряд емкости  $C_Y$ . Высокий уровень сигнала  $D$  (уровень **1**) указывает, что ЗЭ хранил **0**. Далее сигнал  $D$  через разрядно-адресный коммутатор поступает на выход ЗУ.

При записи на линию  $Y$  поступает сигнал  $D$ , соответствующий записываемому двоичному знаку. Затем на линию  $X$  подается высокий уровень сигнала  $CWR$ , открывающий транзистор  $T_1$ , который подключает к линии  $Y$  конденсатор  $C$ . В результате независимо от своего предыдущего состояния емкость оказывается заряженной, если записывается **1**, и разряженной, если записывается **0**.

В ЗУ периодически производится регенерация информации. При регенерации в ЗЭ записывается инверсное значение хранимого до считывания кода. После каждой четной регенерации - его инверсия. В ЗУ имеется схема, сигнал которой указывает, какой код хранить в данный момент ЗЭ - прямой или инверсный.

Динамическая оперативная память **DRAM** — тип памяти, используемый в большинстве систем оперативной памяти современных персональных компьютеров. Основное

преимущество динамической оперативной памяти состоит в том, что ее ячейки упакованы очень плотно, т.е. в очень малый кристалл (микросхему) можно упаковывать много битов, а значит, на их основе можно построить память большой емкости.

Регенерация памяти, к сожалению, "отнимает время" у процессора — каждый цикл регенерации по длительности занимает несколько циклов центрального процессора. В старых компьютерах циклы регенерации могли занимать до 10 % (или больше) процессорного времени, но в современных системами, работающих на частотах, равных сотням и тысячам мегагерц, расходы на регенерацию составляют 1 % (или меньше) процессорного времени.

К сожалению, динамическая оперативная память не отличается высоким быстродействием, обычно она намного медленнее, чем процессор. По этой причине имеется много различных типов организации динамической оперативной памяти, позволяющих улучшить эту характеристику.

### **3. Постоянные ЗУ (ПЗУ, ППЗУ)**

Постоянные ЗУ в рабочем режиме ЭВМ допускают только считывание хранимой информации. В зависимости от типа ПЗУ занесение в него информации производится или в процессе изготовления, или в эксплуатационных условиях путем настройки, предваряющей использование ПЗУ в вычислительном процессе. В последнем случае ПЗУ называются постоянными запоминающими устройствами с изменяемым в процессе эксплуатации содержимым или программируемыми постоянными запоминающими устройствами (ППЗУ).

Постоянные ЗУ обычно строятся как адресные. Функционирование ПЗУ можно рассматривать как выполнение однозначного преобразования  $k$ -разрядного кода адреса ячейки запоминающего массива ЗМ в  $n$ -разрядный код хранящегося в ней слова.

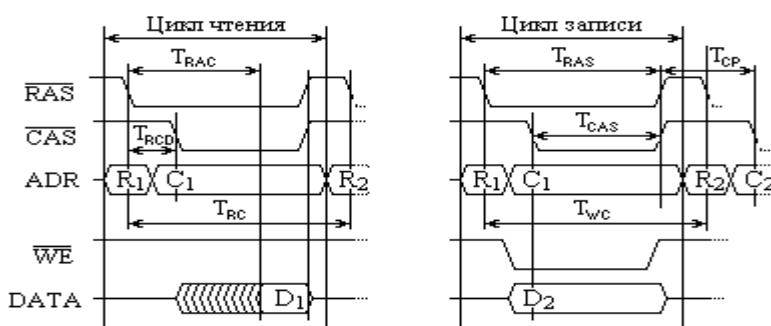

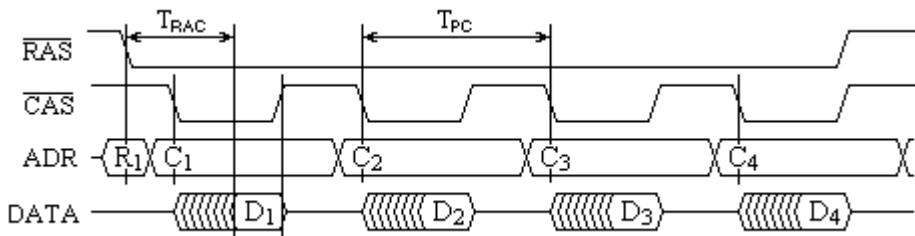

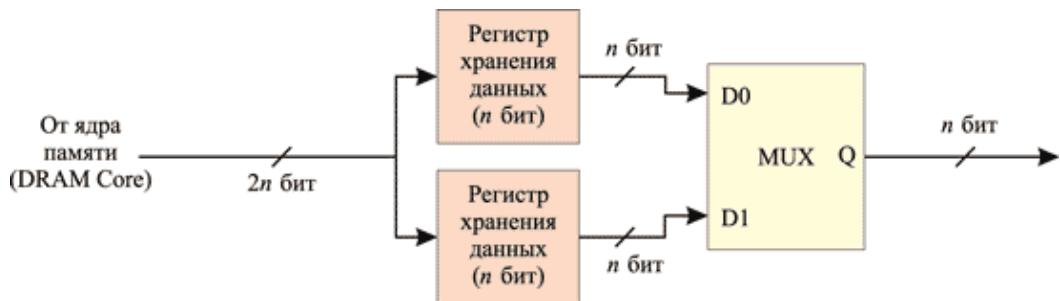

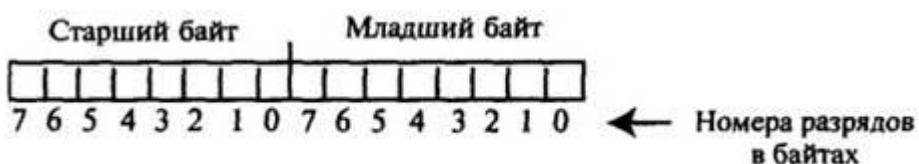

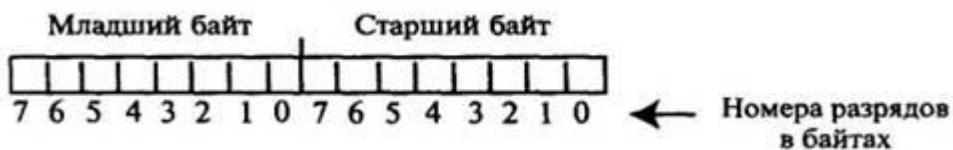

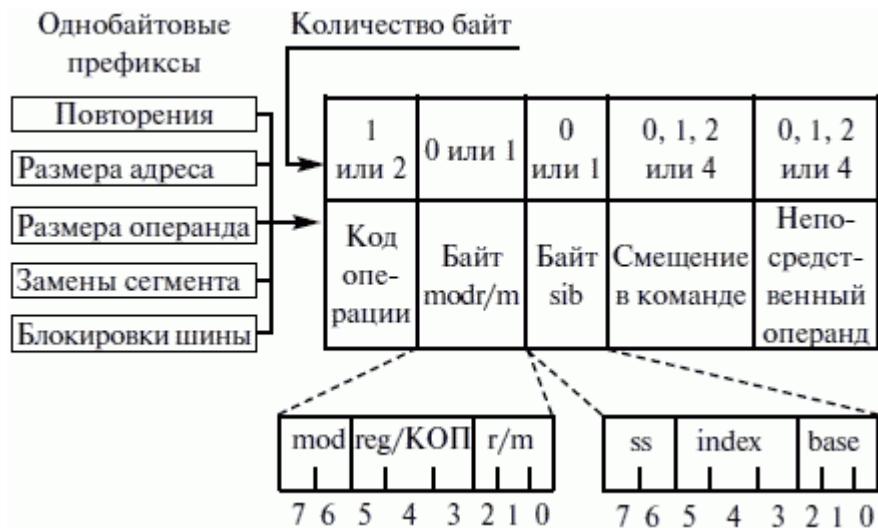

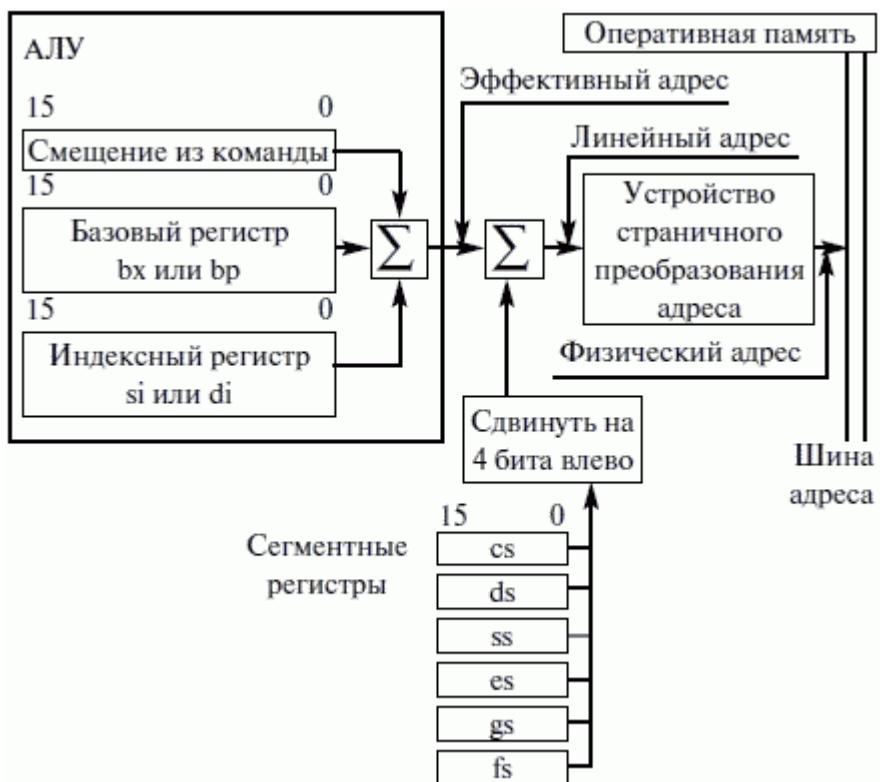

По сравнению с ЗУ с произвольным обращением, допускающим как считывание, так и запись информации, конструкции ПЗУ значительно проще, их быстродействие и надежность выше, а стоимость ниже. Это объясняется большей простотой ЗЭ, отсутствием цепей для записи вообще или, по крайней мере, для оперативной записи, реализацией неразрушающего считывания, исключающего процедуру регенерации информации.